# CALSIM: A COMPUTER HARDWARE DESCRIPTION LANGUAGE FOR COMPUTER SCIENCE EDUCATION SKELTON, WILLIAM ARGLE, JR.

ProQuest Dissertations and Theses; 1982; ProQuest Dissertations & Theses Global

#### INFORMATION TO USERS

This reproduction was made from a copy of a document sent to us for microfilming. While the most advanced technology has been used to photograph and reproduce this document, the quality of the reproduction is heavily dependent upon the quality of the material submitted.

The following explanation of techniques is provided to help clarify markings or notations which may appear on this reproduction.

- 1. The sign or "target" for pages apparently lacking from the document photographed is "Missing Page(s)". If it was possible to obtain the missing page(s) or section, they are spliced into the film along with adjacent pages. This may have necessitated cutting through an image and duplicating adjacent pages to assure complete continuity.

- 2. When an image on the film is obliterated with a round black mark, it is an indication of either blurred copy because of movement during exposure, duplicate copy, or copyrighted materials that should not have been filmed. For blurred pages, a good image of the page can be found in the adjacent frame. If copyrighted materials were deleted, a target note will appear listing the pages in the adjacent frame.

- 3. When a map, drawing or chart, etc., is part of the material being photographed, a definite method of "sectioning" the material has been followed. It is customary to begin filming at the upper left hand corner of a large sheet and to continue from left to right in equal sections with small overlaps. If necessary, sectioning is continued again—beginning below the first row and continuing on until complete.

- 4. For illustrations that cannot be satisfactorily reproduced by xerographic means, photographic prints can be purchased at additional cost and inserted into your xerographic copy. These prints are available upon request from the Dissertations Customer Services Department.

- 5. Some pages in any document may have indistinct print. In all cases the best available copy has been filmed.

University Microfilms International 300 N. Zeeb Road Ann Arbor, MI 48106 Skelton, William Argle, Jr.

# CALSIM: A COMPUTER HARDWARE DESCRIPTION LANGUAGE FOR COMPUTER SCIENCE EDUCATION

The University of Texas at Arlington

PH.D. 1982

University

Microfilms

International 300 N. Zeeb Road, Ann Arbor, MI 48106

by

Skelton, William Argle, Jr.

All Rights Reserved

## PLEASE NOTE:

In all cases this material has been filmed in the best possible way from the available copy. Problems encountered with this document have been identified here with a check mark  $\sqrt{\phantom{a}}$ .

| 1.  | Glossy photographs or pages                                                      |

|-----|----------------------------------------------------------------------------------|

| 2.  | Colored illustrations, paper or print                                            |

| 3.  | Photographs with dark background                                                 |

| 4.  | Illustrations are poor copy                                                      |

| 5.  | Pages with black marks, not original copy                                        |

| 6.  | Print shows through as there is text on both sides of page                       |

| 7.  | Indistinct, broken or small print on several pages                               |

| 8.  | Print exceeds margin requirements                                                |

| 9.  | Tightly bound copy with print lost in spine                                      |

| 10. | Computer printout pages with indistinct print                                    |

| 11. | Page(s) lacking when material received, and not available from school or author. |

| 12. | Page(s) seem to be missing in numbering only as text follows.                    |

| 13. | Two pages numbered Text follows.                                                 |

| 14. | Curling and wrinkled pages                                                       |

| 15. | Other                                                                            |

University

Microfilms

International

CALSIM: A COMPUTER HARDWARE DESCRIPTION

LANGUAGE FOR COMPUTER SCIENCE EDUCATION

by

WILLIAM ARGLE SKELTON, JR.

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

September 1982

CALSIM: A COMPUTER HARDWARE DESCRIPTION LANGUAGE FOR COMPUTER SCIENCE EDUCATION

APPROVED:

Copyright by W. A. Skelton 1982

All Rights Reserved

DEDICATED TO

Tillie, Andy, and Sandi

#### **ACKNOWLEDGEMENTS**

I wish to express my appreciation to each of the professors who have helped me during this effort, Dr. Walker who suggested the project to me, for the three years he served as my advisor and for his unwavering confidence that I would some day finish the effort. I am deeply indebted to Dr. Underwood for assuming responsibility for supervision of the project in mid-stream. Without his interest and leadership in the final phases of my research and thesis preparation, the work would never have been completed.

The idea of using formal grammar and the LALR system to develop cohesive grammars for the Description Language and the simulator driver, I owe to to Dr. Schember. The course work under Dr. Sparr gave me the understanding needed to organize the data handled in the system. The comments of Drs. Carroll and Sparr during the review of my work have been particularly helpful. My thanks to Drs. Buckles and Elizandro for their interest in the project.

My family gave me great support during this effort, particularly Sandi for typing, proofreading and suggestions. My greatest debt is to my wife, Tillie, who has exhibited uncommon patience, understanding, and unfailing support over these many years.

September 10, 1982

#### ABSTRACT

CALSIM: A COMPUTER HARDWARE DESCRIPTION

LANGUAGE FOR COMPUTER SCIENCE EDUCATION

Publication No.

W. A. Skelton, Ph.D.

The University of Texas at Arlington, 1982

Supervising Professor: Stephen Underwood

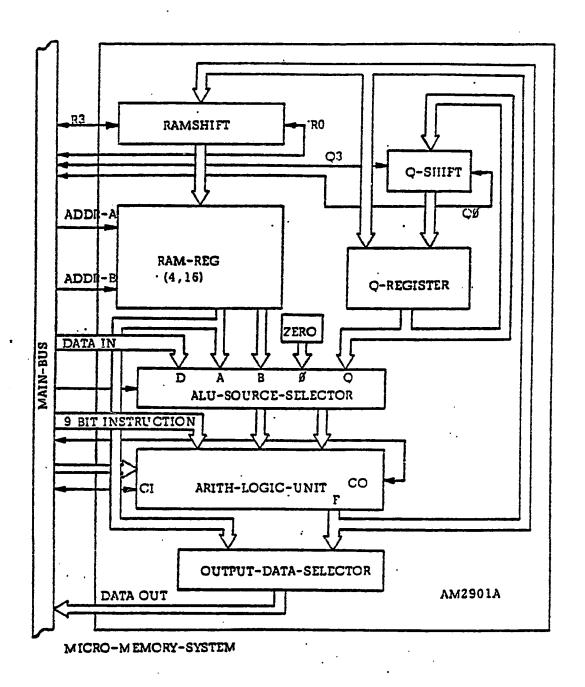

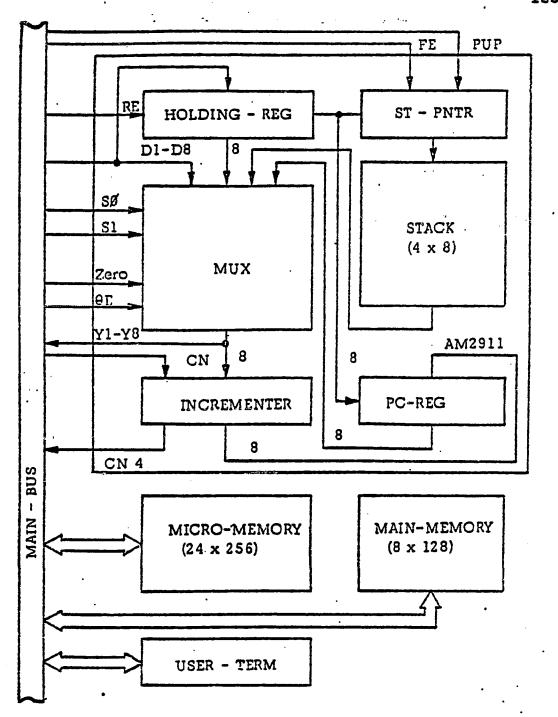

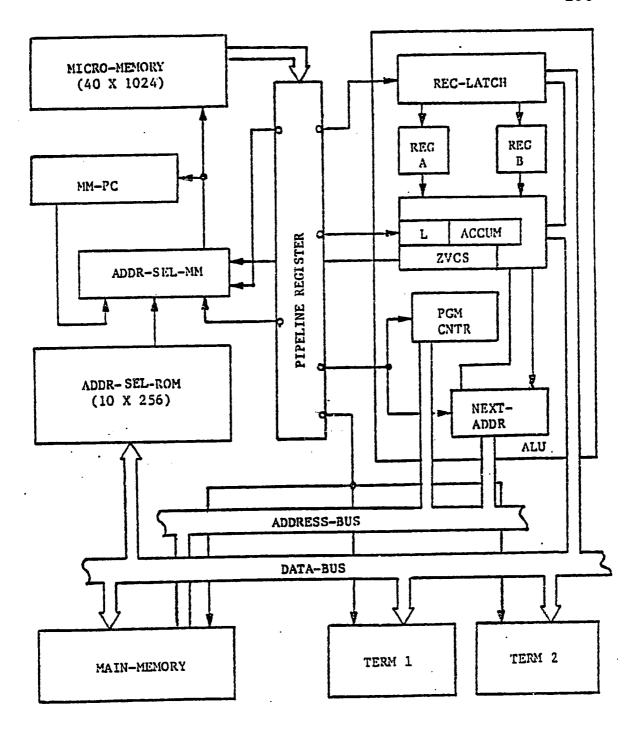

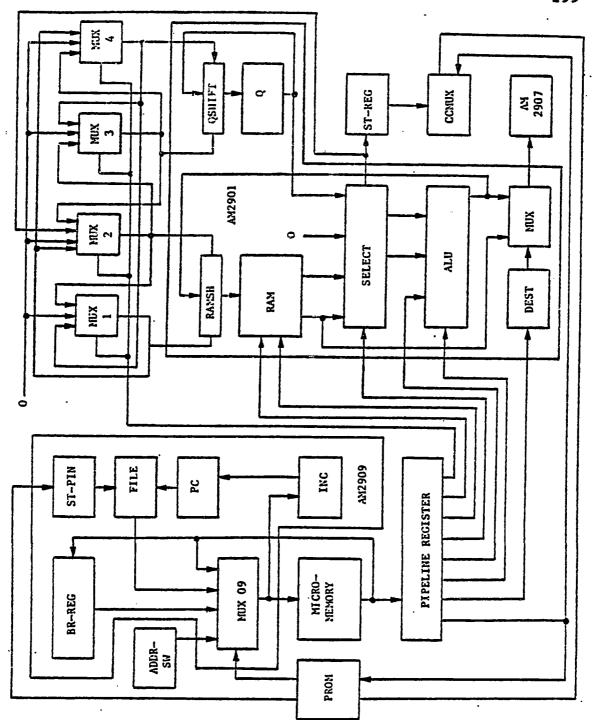

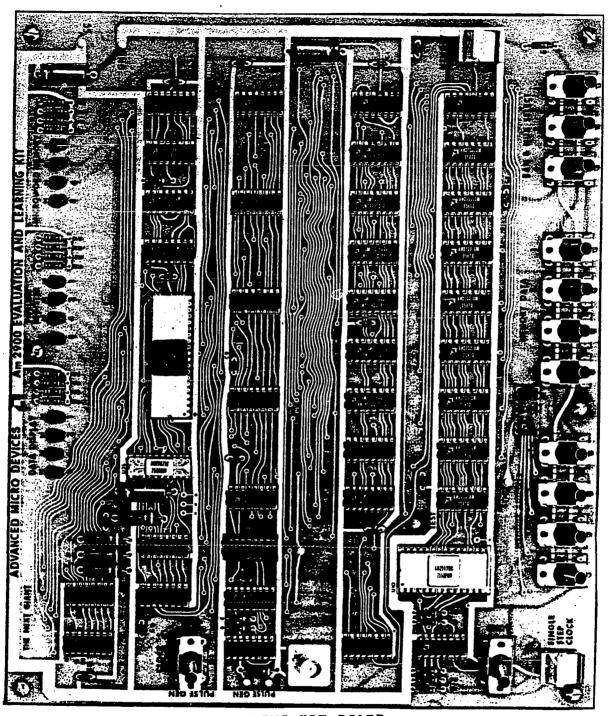

A computer hardware description language (CHDL) and its compiler/simulator system, designed for student use at graduate and undergraduate levels are described. The system is usable above the switching circuit level and incorporates features to investigate designs using microprogrammable components including bit-sliced chips such as the the AMD-2900.

The order of execution in the simulator is controlled by an event table using each time/component as a separate event. The handling of event timing for items copied from the library of components is unique in that the individual times may be changed as they are copied into the active file. The system also allows the user to make several copies with a single statement and adjust the timing of each copied item separately.

The LALR formal grammar, presented in the Appendix, was developed to make the English-like language follow as closely as possible the hierarchic structure of the system being described. This supports a hierarchic design process through the sytem, programming and register transfer levels. Use of the language below the bit level has not been investigated.

The contents of the main memory, micromemory and up to three (3) auxiliary memories are developed separately and read from files into the program memory prior to simulation. The simulation driver incorporates breakpoints, trace, display and other tools needed to follow the simulation which may be carried out in either step-wise or run-to-break fashion. The interactive system is written in Cobol and resides on the DEC-20.

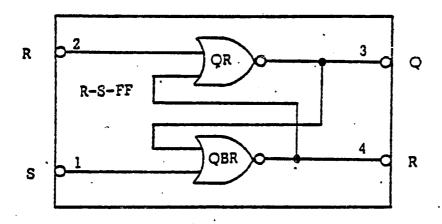

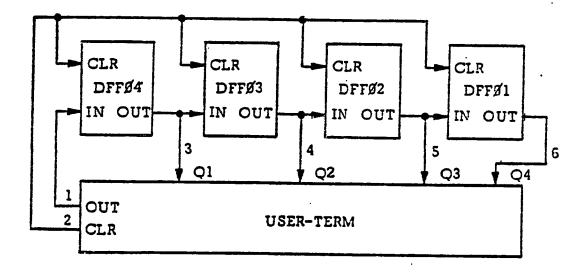

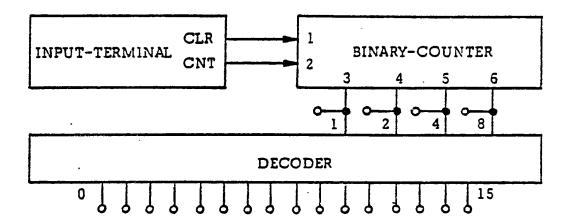

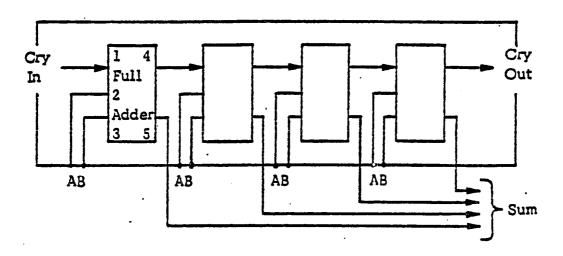

The system has been used one semester for a graduate course in computer organization. The User's Manual (Appendix 6) contains examples from flip-flops to microprogramming and show examples, diagrams, explanations, and coded descriptions of the logical device.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS |                |              |            |             |          | •          | •   | •          |         |            |           |             |                 |         |              |     |       |     |    |          |

|------------------|----------------|--------------|------------|-------------|----------|------------|-----|------------|---------|------------|-----------|-------------|-----------------|---------|--------------|-----|-------|-----|----|----------|

| ABSTRACT         | r              | . •          | •          | • •         | •        | • •        | •   | •          | •       | •          | •         | •           | • •             | •       | •            | •   | •     | •   | •  | ٧        |

| Chapter          |                |              |            |             |          |            |     |            |         |            |           |             |                 |         |              |     |       |     |    |          |

| I. IN            | rroduc         | CTIO         | N.         | • •         | •        | • •        | •   | •          | •       | •          | •         | •           | •               | •       | •            | •   | •     | •   | •  |          |

|                  | Backg          | roui         | nđ.        |             | •        |            | •   | •          | •       | •          | :         | •_ •        | •               | •       | •            | •   | ٠     | •   | •  | :        |

|                  | Premi          | .ses         | on         | Wh:         | ich      | th         | e 9 | Sys        | te      | m .        | is        | D€          | SI              | .gn     | ed           | •   | •     | •   | •  |          |

|                  | Class          | ific         | cati       | Lon         | OĪ       | CH         | DL' | S          | •       | •          | • .       | ٠ ،         | · •             | •       | •            | •   | •     | •   | •  |          |

|                  | Compa          | tea          | use<br>S   | ; IC        | 75 T     | cne        | + c | ing        | ua      | ge<br>n    | מנ<br>מכר | .1U<br>1] = | oy<br>T         | CH      | יונט.<br>דרו | 's  | •     | •   | •  |          |

|                  | Time           | Doce         | )!! C      | ייר<br>יידר | Sv       | 2 TIII     | m f | For        |         | מט<br>יע   | iec       | 3 7         |                 | ms      | ىدىد.        | ٠   | •     | •   | •  | ě        |

|                  | Other          | rese<br>test | - and      | ing<br>sior | ns<br>ns | for        |     | omr.       | 11t.    | op.<br>er  | Sc        | iie         | nc              | e       | Ed           | uca | iti   | lon | ١. | -        |

|                  | The S          | oftv         | vare       | S           | ıpp      | ort        | Sy  | st         | .em     | _          | Ūs        | ser         | 's              | V       | ie           | wpo | ) i r | ıt  | •  | 8        |

| II. HAR          | RDWARE         | DES          | CRI        | PT:         | ION      | LA         | NGU | JAG        | ES      | •          | •         |             | •               | •       | •            | •   | •     | •   | •  | ç        |

|                  | What           | Are          | Har        | dwa         | are      | De         | sci | ip         | ti      | on         | La        | anç         | jua             | .ge     | s            | ?.  | •     | •   | •  | 9        |

|                  | Proli          |              |            |             |          |            |     |            |         |            |           |             |                 |         |              |     |       |     |    | 12       |

|                  | An Ov          | ervi         | Lew        | of          | CH       | DL'        | s.  | •          | •       | •          | • •       |             | . •             | •       | •            | •   | •     | •   | •  | 15       |

|                  | Anato          | my c         | of_a       | He          | ard      | war        | e_[ | es)        | cr.     | ip         | tic       | on          | La              | ng      | ua           | ge  | •     |     | •  | 16       |

|                  | Eleme<br>Speci | nts<br>al F  | ot<br>Prob | Soi         | ns '     | are<br>wit | b E | ipp<br>Bit | or<br>S | t :        | sys       | Ha          | ms              | I<br>wa | re           | •.  | •     | . S | •  | 22<br>28 |

| III. MIC         | ROPRO          | GRAM         | (MIN       | IG 8        | k M      | ICR        | OPF | ROG        | RAI     | MM:        | INC       | 3 S         | UP              | PO      | RT           | SY  | SI    | 'EM | S  | 32       |

|                  | Histo          | rica         | al R       | levi        | Lew      |            |     |            |         | •          |           |             |                 |         |              | •   |       |     |    | 32       |

|                  | Uses           | of t         | he         | Mic         | ro       | pro        | gra | ımm        | ing     | <b>a</b> ( | Cor       | ice         | pt              | •       | •            | •   | •     |     |    | 33       |

|                  | MOS V          | ersu         | ıs B       | lipo        | ola:     | r T        | ech | ıno        | 100     | JY .       |           | •           | •               | •       | •            | •   | •     | •   | •  | 34       |

|                  | Assem          | bly          | of         | Mic         | ro       | cod        | e.  | •          | •       | •          |           | •           | •               | •       | •            | •   | •     | • . | •  | 36       |

| IV. CAL          | SIM:           | COM          | 1PUT       | 'ER         | AR       | CHI'       | TEC | TU         | RE      | L          | ANG       | JUA         | GE.             | F       | OR           |     |       |     |    |          |

|                  | SIMUL          |              |            |             | •        | • •        | •   | •          | •       | • (        |           | •           | •               | •       | •            | •   | •     | •   | •  | 37       |

|                  | Proje<br>The R | ct E         | Back       | gro         | oun      | d.         | •   | •          | •       | •          |           |             | •               |         | •            | •   | •     | •   | •  | 37       |

|                  | TheR           | equi         | rem        | ient        | s        | for        | th  | e          | Gra     | 3.MI       | nar       | •           | •               | •       | •            | •   | •     | •   | •  | 38       |

|                  | The G          | ramm         | nar        |             | De:      | vel        | mgo | ien        | t .     | • •        |           | •           | •               | •       | •            | •   | •     | •   | •  | 42       |

|                  | The G          |              |            |             |          |            |     |            |         |            |           |             |                 |         |              |     |       |     | •  | 44       |

| V. SIM           | CAL:           | THE          | SOF        | TWA         | RE       | CO         | MPI | LE         | R/S     | SIN        | /UI       | ÆΤ          | OR              | S       | YS'          | rem |       |     | •  | 46       |

|                  | The R          | equi         | .rem       | ent         | s        | for        | th  | e          | Sug     | ogc        | ort       | S           | ys <sup>.</sup> | te      | n.           | •   | •     | •   |    | 46       |

|                  | The C          | onst         | ruc        | tio         | n c      | of t       | the | S          | oft     | .wa        | ıre       | s           | upj             | po:     | rt           | Sy  | st    | em  | •  | 50       |

|                  | The S          | oftw         | are        | su          | ppo      | ort        | Sy  | st         | em      |            | · I       | mp          | ler             | nei     | nta          | ati | on    | •   | •  | 54       |

| VI. A P          | ROPOS          | AL F         | OR         | USE         | I        | T T        | EAC | ΗI         | ŊĠ      | CC         | MP        | UT:         | ER              | S       | CIE          | ENC | E     | •   | •  | 56       |

| 1                | The P          | ropo         | sal        | •           | •        | •          | •   | •          |         | •          | •         | •           | •               | •       | •            | •   | •     | •   | •  | 56       |

| Use i<br>Use i<br>Use i                                           | duction t<br>n the Stu<br>n Study o<br>n Applica<br>Experier                                                                                                                    | ndy of<br>of Mic<br>ation                                       | CPU<br>ropr<br>Proq                       | 's a<br>ogra<br>ram | nd M<br>mmin<br>Desi                         | licro<br>.g .<br>.gn S        | opro<br>•••<br>Stud                     | cess<br>          | ors                        | •        | •                                       | 62<br>62<br>63                                                                          |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------|---------------------|----------------------------------------------|-------------------------------|-----------------------------------------|-------------------|----------------------------|----------|-----------------------------------------|-----------------------------------------------------------------------------------------|

| VII. CONCLUSIO                                                    | ONS AND I                                                                                                                                                                       | POSSIE                                                          | BLE E                                     | XTEN                | SION                                         | ıs .                          |                                         |                   | •                          | •        | •                                       | 66                                                                                      |

| Softw<br>Appli                                                    | m Testing<br>are Syste<br>cation of<br>ry                                                                                                                                       | em Exp<br>Meth                                                  | ansi<br>nodol                             | ons<br>ogy          | <br>to 0                                     | <br>Other                     | <br>r Ar                                | . eas             | •                          | •        | •                                       | 66<br>68<br>75                                                                          |

| Appendix                                                          |                                                                                                                                                                                 | • •                                                             |                                           |                     | • •                                          |                               |                                         |                   | •                          | •        | •                                       | 76                                                                                      |

| 1. CHARACTER                                                      | ISTICS OF                                                                                                                                                                       | SIX                                                             | (6)                                       | CHDL                | 'S v                                         | ersi                          | ıs C                                    | ALSI              | М.                         | •        |                                         | 77                                                                                      |

| 2. SUMMARY O                                                      | F COMPUTE                                                                                                                                                                       | ER HAF                                                          | RDWAR                                     | E DE                | SCRI                                         | PTIC                          | ON L                                    | ANGU              | JAGE                       | s        | •                                       | 79                                                                                      |

| 3. THE FORMA                                                      | L GRAMMAF                                                                                                                                                                       | OF C                                                            | ALSI                                      | м.                  |                                              |                               |                                         |                   | •                          | •        | •                                       | 97                                                                                      |

| 4. INDEX TO                                                       | RESERVED                                                                                                                                                                        | WORDS                                                           | USE                                       | D IN                | CAL                                          | SIM                           | GRA                                     | MMAF              | ₹.                         | •        | . ]                                     | 103                                                                                     |

| 5. TRIAL GRAD                                                     | MMAR OF N                                                                                                                                                                       | IANUFA                                                          | CTUR                                      | ING                 | DESC                                         | RIP                           | rion                                    | LAN               | IGUA                       | \GE      | . ]                                     | 108                                                                                     |

| 6. USERS' MA                                                      | NUAL FOR                                                                                                                                                                        | CALSI                                                           | M/SI                                      | MCAL                | • •                                          |                               |                                         |                   |                            | •        | . ]                                     | 111                                                                                     |

| 2.0 Get<br>3.0 The<br>4.0 The<br>5.0 Prej<br>6.0 Usin<br>7.0 Appo | roduction ting Star Calsim I Calsim G paring th ng the Si endices Calsim Re Simulator Examples Appendix Appendix Appendix Appendix Appendix Appendix Appendix Appendix Appendix | ted wanguate Desimoal eserve in the 3.1 3.2 3.3 3.4 3.5 3.6 3.7 | vith age. ar sign Soft  ed Wo erfac ae Ca | Cals                | im/S Hard sup and serv /Sim ps. an ers, hmet | Symbolic I code Full Proputer | De De Sy Dols Nord Sys Dift A Logi gram | scri<br>stem<br>s | pti<br>ist<br>code<br>sit( | on<br>er | . ] . ] . ] . ] . ] . ] . ] . ] . ] . ] | 116<br>120<br>139<br>140<br>146<br>158<br>159<br>164<br>167<br>167<br>167<br>169<br>184 |

| WORKS CITED.                                                      |                                                                                                                                                                                 | • •                                                             | • •                                       |                     |                                              |                               |                                         |                   | •                          | •        | . 2                                     | 201                                                                                     |

|                                                                   | TEC .                                                                                                                                                                           |                                                                 |                                           |                     |                                              |                               |                                         |                   |                            | _        | . 2                                     | 11                                                                                      |

## CHAPTER I

#### INTRODUCTION

# Background

Although microprogramming dates from the early fifties (107), and Computer Hardware Description Languages (CHDL's) date from the early sixties (24), effort to adapt the CHDL's for use with bit-sliced microprogrammable computer architecture design and development has not been entirely successful (92). To a large extent, each area has developed separately serving the technology of the time in it's own way. A Computer Hardware Description Language and software support system is described here which adapts the technology of the CHDL's for use in design studies using bit-sliced components. Since the system is usable as low as the bit level, it can be used for Computer Science education courses from Computer Organization to Microprogramming.

An increase in the use of bit-sliced components for application hardware was predicted for the eighties (75). The families of bipolar, bit-sliced components offers the developer more design freedom and a better organized approach than conventional computer architectures (14).

These are available from sources such as the Advanced Micro Devices AMD-2900 or Texas Instrument SN-74S481 (2).

However, as Alexandrididis (5) states, "The advantages of bit-sliced microprocessors are not free -- they require a serious investment in system support software". Currently, application designs using bit-sliced hardware are developed using custom software, simulators, and prototypes supported by extensive hardware monitoring tools (29). This high initial cost of support hardware and the prospect of preparing custom software causes many designers to avoid approaches using bit-sliced technology (5) and precludes extensive use in Computer Science Education where funds may be limited.

It is evident that the CHDL's have not met the need for development software since more expensive methods are still widely used (1), both in industry and Computer Science education. Several reports, however, have been published on the use of CHDL's in Computer Science education (19), (23), (40), (99) and others have addressed the use of CHDL'S for applications with bit-sliced hardware (43), (50), (72).

Premises on Which the System is Designed

The extensions and differences of Calsim (Computer Architecture Language for Simulation) and its software

system from existing CHDL's were developed based on three premises. First, a change will occur in the eighties in the fundamental way logical devices are designed due to the increased size of the chips available. Bit-sliced chips are predicted to be among those which will have increased use (2). Second, increased emphasis should be placed on the use of these components in Computer Science Education. Third, the best way to teach this subject is to use a CHDL for all Computer Science courses where a CHDL is applicable.

# Classification of CHDL'S

The primary method of classifying CHDL'S is by the level of abstraction of the language. This has varied from four to seven levels by different workers in the field. Throughout this treatise, five levels will be used as reported by Barbacci (14) -- PMS (roughly equivalent to system) programming, register transfer, switching circuit (roughly equivalent to gate), and circuit level.

CHDL'S may be intended primarily for either simulation at a particular level of design or the generation of design details below the level described. Each of these may also be further divided depending on the level of abstraction.

Hardware language also vary depending on the intended user -- academic, industry, with further divisions under

each. Obviously the more detail that is incorporated into a model, the more expensive it will be. Cost is reflected in all aspects of the system: software cost, operation and maintenance cost, user learning time, and the time required for the user to develop the hardware description.

Many of the CHDL'S also address specific problems or portions of computer technology -- input/output, graphics, asynchronous operation, timing problems. Lastly the various CHDL'S reflect the technology of the time in which they were developed, changing their emphasis as technology changes.

Each CHDL will be usable over only a portion of this broad area; usually there are secondary uses on the fringe of the primary uses. There is no universal CHDL, however.

Targeted Use for the Language and the System

The system presented here is designed for the register transfer, programming, and system levels and specifically addresses microprogramming capabilities, use of multiple and bit-sliced components. The language reflects the current technology using the LSI as the basic building block and is intended for simulation studies in Computer Science from micro-programmable system designs through flip-flops in an interactive system.

The system description is hierarchic and supports a

hierarchic design process, thus allowing successive examination at system, programming and register transfer levels. Hierarchic design is discussed by vanCleemput (100).

Comparison of Calsim to Six Popular CHDL'S

Appendix one (1) compares Calsim with six currently popular languages. These were chosen to represent various types available and to more clearly define the position of Calsim in the broad area of CHDL uses. Calsim is shown in the middle of the table with "\*\*" at items where the difference is significant. A brief discussion of the differences follow.

The time event table uses both a time event, as commonly used in simulation languages such as SIMSCRIPT combined with the part component number. Since a time 'RESET' is also available, branching can be accomplished easily. The need for "major labels" and branching was pointed out in (49).

Memory handling in Simcal requires that the memory content be read from a file and further provides for both micromemory and up to three (3) other memories to also be read into the simulator's main memory.

Special syntax is used by Calsim to describe the type of data being sent or received so that conversion at the

simulators terminal will be in readable characters. The port (terminal) descriptions in Simcal allow the user to specify the type of data expected from the port or is being sent to the port. The simulator converts the data to or from Ascii so that it is readable if outputted or can be inputted as Ascii and sent to the computer in its correct format. Heath, Carroll, and Cwik discuss the need for data conversion of simulation output in terms of a postprocessor (49); this idea has been adapted to an interactive system.

# Time Resetting System for Copied Items

The nature of the targeted system demanded that the library utility facilitate copying groups of components with minimum difficulty. Since no method of handling the problem could be found in other systems, the multiple copy command It is available in addition to the command was developed. which allows the user to suffix a component name. As component copied may have several time events within its description, the copy command was then modified to allow both multiple times within the component description to be either replaced or modified as well as allowing several replicates to be made by a single statement. The details of the library and time resetting systems are discussed in sections 3.10 AND 3.11 of the Users' Manual (Appendix 6).

- 1. Calsim offers the user freedom to represent the machine being studied without being bound to preconceived patterns of computer architecture, such as the fetch/execute cycle. See (44) and (100).

- 2. Calsim faithfully represents the physical organization down to the bit level and may be used at the gate level. Most register transfer CHDL'S give this aspects get little attention. This principle is discussed at by Borrione in (18) and Bressy in (19).

- 3. Calsim resembles English to a much greater extent than most other CHDL's. Although Chu stated in the early sixties that CHDL's should resemble a natural language (28), most of the CHDL'S are more cryptic than a natural language.

- 4. The data conversion available in the I-O chip has already been discussed. Calsim also allows logical action within the chip and allows the port to be "tied" to a file so that data can be transmitted to and from a file directly. Important aspects of input-output are discussed by Parker and Wallace in (77) and (102).

5. Since Calsim must operate at the bit level to fulfill its intended purpose of manipulating the bit patterns throughout a microprogrammable machine, data types are not used. The user, of course is always free to "build" data types into his hardware design.

The Software support System -- User's Viewpoint

The software support system used with Calsim is called SIMCAL (Simulator for Computer Architectural Language). contains four primary sections in an interactive environment which follow the pattern found in most software support systems for CHDL's. The compiler verifies the syntax of the description, converts the English-like language of the hardware description into tables and checks for errors omissions. The second section, a simulator driver, interfaces the user to the simulator, providing extensive user support for controling execution and showing status of the simulated logical device. The third component, the tor itself, carries out the actual simulations commanded by the user in the simulator driver, stopping at break points as instructed. The last part embraces the support programs Library, Help, Table Preparation, and Documantation, Memory Read-in.

### CHAPTER II

## HARDWARE DESCRIPTION LANGUAGES

What are Hardware Description Languages?

In every specialized field, one finds unique ways of expressing thoughts, designs and ideas. So in a broad sense "Development of Computer Hardware Description Language's (CHDL's) began at the same time as the birth of the computer" (72). In 1964, Schorr (88) stated "No adequate way of describing a digital system in terms of sequential circuit theory, nor to present this information to a computer, is known". He then suggested a register transfer language as a way of coping with the "Heuristic methods of design". The same year a formal language called LOTIS (Logical Language for Timing and Sequencing) was proposed by Schlaeppi (87). He suggested that software could be prepared to use the semantic output from syntactical analysis of the language to both simulate performance and to synthesize circuits.

In 1965, Chu (26) proposed another language in his report on CDL (Computer Design Language). He used a level of abstraction, just above the electronic component level, now

commonly referred to as "Register Transfer Level" to accomplish his stated purpose "To bridge the gap between hardware and software design".

Since then, the proposed uses of CHDL's have greatly expanded and one finds with this expansion, invention of new names for the term CHDL -- ADL (Architectural Description SDL (System Design Language), HDL (Hardware Language), Whatever the generic Description Language) among others. name and specialized or extended uses, they are generally considered a CHDL by the Computer Scientists working in the In addition to communication among the designers studying a system, the CHDL's are expected to communicate to a computer sufficient data to create a simulator for the described hardware and automatically generate the circuits below the level described as proposed by Schlaeppi (87). Needless to say, these requirements greatly affect form and content of the proposed languages. See Shiva (89) for a tutorial on CHDL'S.

The languages have been classified as either procedural or non-procedural depending upon the syntactic organization and the emphasis on various aspects of the hardware. Vogel proposes a third approach in (103) consisting of a language based on "Mathematical modeling of real-time automation encompassing the concept of time". Lipovski, however takes a simpler view and calls the CHDL's "A variation of a

programming language tuned to the overall needs of describing hardware" (71). Baer (11) states "We can justify CHDL's only because they bring more clarity and impose less complexity in the data and control structure of the specific application". However the difference between CHDL's and programming languages is much more fundamental than indicated by the superficial appearance of the two families of languages.

The difference in purpose between the CHDL's and programming languages is sometimes clouded by the similar constructions of the two. The programming languages are vitally concerned with algorithmic processes; the CHDL's algorithms are limited. The programming languages use complex data structures; the CHDL's data structures are usually limited. The CHDL's must address timing constructively; the programming languages either ignore timing or treat it as a peripheral issue. The CHDL's must be concerned with hardware organization; programming languages do not even contain such a concept and if addressed at all, it must be done by the language user.

The two types of languages use many of the same basic elements to build their structure, just as a car and a truck use the same basic components. The end use, however, is so different that the actual language design must be, or should be affected in numerous important areas.

A complete CHDL addresses both the physical and functional aspects of the hardware. The physical aspects include component names, connectors, number and name of pins, wiring, physical organization, registers, and clocks. The functional aspects include a description of how the logic state within the hardware changes, how the state is stored, and timing of the logic flow. Among the many languages in use, one finds a wide variation in the levels of abstraction, the physical/operational emphasis, the formal syntax and grammar. For the purpose of this report, we will use the following definition of a CHDL.

A Computer Hardware Description Language is a language defined by a formal set of syntactic and semantic rules which can be used to precisely describe significant portions of both the physical and functional aspects of a logical design and will support a simulator, hardware generator or both.

# Proliferation of Hardware Description Languages

CHDL's have been investigated and reported since the early sixties (95), (87). Their value in the areas of design description, organization of design information, teaching of computer science, documentation, automatic

circuit generation and simulation have been recognized and Su has reported on described (24), (59), (60), (76). twenty-one (21) CHDL's in the U.S. (96). More than a dozen languages have been reported by Vaucher and others outside of the U.S., (102). Since publication of those reports in 1974, many additional languages have been reported. has described a language to be used graphically called FLOWWARE (23). Stewart has described a language called LOGAL (Logic Algorithmic Package) and a software system called LADS (Logic Algorithmic Design) (94). Analuf has introduced a language for logic and timing (7), Parker and Wallace have proposed a special input/outout Hardware De-Language (77), (104). Tomek has reported a scription simulation language called HARD (Hardware Simulation in Education) to be used exclusively for teaching Computer Science. (99). These and many others have proposed new to established uses and extensions of the approaches functions the languages perform. See Appendix 2 for a list of the published languages.

Lipovski describes the proliferation of HDL's, called by him the "Tower of Babel", and suggests industry cooperation as a solution to the problem (71). In spite of the obvious problem with multiple languages, they continue to proliferate. Smith recognized this and stated in the beginning of a paper presenting a new language "... the rationale for creating yet another Computer Hardware Description Language in a field already stocked with languages...'(93). (His stated purpose is to reduce dependance on labels, increase readability, and efficiency). Heath, Carroll, and Cwik in (48) stated "CDL was found to be quite cumbersome to use, ..." and then described modification of several CDL constructions. Su states in (98) "The process of transferring a high level computer hardware description language specification of a system into a logic diagram is still in its infancy."

A committee(Conlan), chaired by R. Piloty, was formed to study ways to bring more order and uniformity to CHDL'S, but apparently has been unable to reach an agreement since no publications from the committee were found.

Since the introduction of CHDL'S two decades ago, over 50 additional languages have been proposed and over 200 papers have been published on the topic. Each of the proposed languages extends existing languages to include a new function or addresses an old function in a different way. In many cases the languages are devised to overcome problems reported in the technical journals by workers in the field. Appendix 1 summarizes 50 of the languages discussed in the references and some of the important characteristics of each language. There is no indication that proliferation has abated.

### An Overview of CHDL's

The listing in Appendix 2 illustrates the great variety of Computer Hardware Description Languages which have been written and implemented. The brief discussion of each is intended to give the reader an overview of progress in this field and provide some of the distinguishing characteristics of each language.

The name of each language, usually an acronym, is given first followed by the meaning of the acronym, the authors name and the date of the original article. The references are listed in the order of importance in providing material for the entry. They have been used freely in obtaining direct quotations and paraphrasing for the paragraphs on "Purpose" and "Discussion" of the language.

Each new language developed, presumably, solves a current problem or performs new functions not being performed by existing languages. In some cases the author of the reference material has stated explicitly the purpose of the new language, but in many others the reason for the new language must be inferred from the text of the article. In either case the reason presented in the Appendix is derived from the material in the text of the article to the greatest extent possible.

The "Discussion" paragraph centers around the primary

characteristics and uniqueness of the language and where information is available, implementation. It would be desirable to discuss each language using the same format and exploring the same aspects of the language such as grammar, concurrency, level of abstraction, etc. However, this is not possible as the authors have not discussed the same characteristics in their respective papers. The entry therefore reflects the emphasis used by the author of the reference.

Anatomy of a Computer Hardware Description Language

The question as to what a CHDL is has already been addressed, but no details were provided as to the component parts of the CHDL. We now examine the parts commonly found in a CHDL, restricting the discussion, to the language itself, not it's means of implementation.

Registers, Subregisters, and Cascade Registers: Each CHDL must have a way to declare the existence of certain registers and to specify their sizes. In some languages the user is allowed two dimensions, thus is able to create a series of registers with a common name. The languages use both left to right and right to left numbering of the bit positions, some allowing one, some the other, and a few allowing the user to choose. A single flip-flop is usually

regarded as a one-bit register. The usual form of register description is to use a key word, usually "REGISTER", followed by the dimension(s) in parenthesis. Calsim follows this form, using "REGISTER" followed by the register name with the dimensions in parenthesis. Calsim will accept two dimensions, the first is the bit length; the second is optional and may be used to establish a group of registers with same name to be accessed by subscript.

It is usual to include a means to describe parts of a register as a subregister just as the term is ordinarily used with hardware. A means is also usually present to cascade two or more registers to form a longer register with a new name. Calsim supports both sub and cascade registers using the keywords "SUBREGISTER" and "CASCADE".

Special Registers: Some CHDL's have given special treatment to the registers common to conventional computers such as SP (stack pointer), MAR (Memory Address Register), PC (Program Counter), IR (Instruction Register), MDB (Memory Data Buffer). Since each of the special registers are treated in a special way within the respective software support systems, the user must be aware of the restrictions on the system in use and its implication during simulation. Since Calsim, like several other languages, makes no assumptions as to architecture, it uses no special registers.

the CHDL's seem to be divided into two groups, one emphasizing the CPU portion of a computer with other devices as appendages to the CPU and the second is more system oriented. Many of the first were developed to synthesize the internal circuits in the CPU. The second group of languages perform these same functions and also allow grouping of the logical components at several levels using some type of connection or communication between the components. Calsim is the latter type allowing up to 99 levels of hardware descriptions, thus directly supporting a hierarchical design process as described by vancleemput (100). However, Calsim will not support design descriptions below the register transfer level.

Connectors: In many register transfer languages, the values can be transferred and tests made without regard to actual hardware connections; they are assumed to exist. Languages like Calsim, which accept hierarchical descriptions, also perform in the same manner within each component description. Between components, however the connectors must be declared, and a means of communication established between the chips. Calsim does this by describing the connectors in a "CONNECTION" statement and connecting the components to each other with a "WIRING" statement.

Signals: The signals in most CHDL's are only 0 and 1, but in few languages the signal may also be defined as "unknown", "high impedance", or "open"; Calsim permits four states, combining "high impedance and "unknown". Values of zero and one have the usual meaning as used in hardware descriptions. Wires not connected to any component are "open".

Data Types: All programming languages allow the user to specify by some means the data type of variables and stored characters. Most languages have integers, character, and floating point formats and may also include double precision and some type of packed decimal or BCD. In those CHDL's which are closely related to programming languages, these same data types are usually present. In other languages such as CDL and Calsim, where such types would mask the primary objective of the language, data types are not used. All data is simply strings of zeroes and ones. Calsim, however, provides for data types associated with each port (terminal) so that conversion to/from ASCII format at the simulated terminal is accomplished.

I-O and Terminals: If the terminal in the "designed" machine is an ASCII terminal, then some action in the machine or program being simulated will have produced a conversion to the ASCII format. Ports or terminals which are

used for input or output of other formats such as BCD must be converted if they are to be displayed properly at the ASCII terminal interfacing the DEC-20. It is not desirable to require the user to make the translation himself. If a design, for example, includes a series of ports reading BCD, the user should be able to introduce at the proper point in simulation a series of numbers values which would be converted to BCD by the simulator.

Timing: A wide variety of approaches to timing have been used by CHDL's. The most simple approach is to use each statement (in a procedural CHDL) as a "tick" of the clock and advance the timing one cycle. The simulation then progresses through the instructions just as execution of a program progresses through the instructions. Such languages usually allow looping, and "GO TO" statements of various types which is equivalent to resetting the clock. Many variations of this basic idea have been used.

calsim uses an event clock which the user must set for each executable component. The active components may have simulated concurrent operations, and each component may use several events. Resetting may be called for in the hardware description language or it may be dynamically reset during simulation as the result of a test. The Calsim system allows the user to "HOLD" by the looping just described.

Concurrency: If a CHDL supports concurrency, additional checking must be performed during simulation. This is handled in a variety of ways, but they all involve setting flags of some type to assure that all actions have been taken before proceeding to the next step. Closely connected with this, is the handling of asynchronous operations. In some cases the language must provide special construction to escape its fetch/execute cycle so interrupts can be serviced in an asynchronous manner.

The Calsim/Simcal system uses an event table in which any number of active components can share one or more Those operations are then carried out in the order entered, but no data is placed on the connectors to/from the component until all of the components sharing a time event have completed execution. If there is data being passed between two or more components as they execute concurrently, then smaller time slices are used to further divide the time long series of operations must occur in a Ιf increments. one or more components, then these can be listed under a single timed event, thus precluding the transfer of the signals to the connectors until both components have completed the computations.

Storage/Retrieval of Prechecked Descriptions: Several languages contain "MACROS" which are closely akin to the

same item found in assembly languages. Calsim does not use Macros in that sense, but uses a "COPY FROM LIBRARY" concept as found in high level language compilers. In Calsim, a library of components may be written, prechecked, and stored; then copied from the library into the hardware description.

The copy clause has been extended to allow the user to make multiple copies of the item, a situation found in most designs, but particularly in those supporting bit-sliced components. As the items are copied two digits are affixed to the end of the name giving each a unique identity. An alternate method allows the user to add a suffix to the component identifier.

Calsim also allows the user to adjust the time found within the items copied. This may be done even when there are several times within the item and when several items are copied with a single statement.

Elements of Software support Systems for CHDL's

If a CHDL is to do more than provide communication among personnel, a software support system must be prepared which will read the language and perform functions in response to the description. It is usually prepared following the language design rather than concurrently with it and

must perform one or more of several functions. The software may be designed for batch use or for interactive support; it may be a single program or a group of programs; may provide little or significant support. A description of these functions with special attention to the support software for Calsim follows.

Compilation: Compilation is widely recognized as consisting of three tasks (6), namely:

- (1) Lexical Scanning.

- (2) Syntactical Analysis.

- (3) Generation of Semantic Output.

The hardware description language compilers follow the same form and like the programming languages must output both data structure and executable code. In the seventies, the grammar of programming languages came to be understood well enough that syntax directed compilers could be written which would be driven by tables from grammar analyzers (6). The compiler writer still must prepare the lexical scanner, a relatively simple task, copy the syntax algorithm and provide the semantic output statements. Although the semantic output, by far the largest of the tasks, still must be prepared, the task is now highly structured into small

manageable pieces. The Calsim compiler was developed using the LALR grammar analyzer by LaLonde of the University of Toronto (63) and residing on the UTA IBM-4341.

Interpretation: Interpretive languages, such as APL, must perform the same syntactic checks as are performed in compilation, but tables are not created from the description. The incoming code is executed directly. In such cases data items have been previously declared, with storage already established.

Simulation: Even though several functions other than simulation may be performed by software for a CHDL, the software may be referred to as a simulator. The discussion here will be centered on the simulation itself, not the other functions. The simulator actually performs two (2) separate and distinct functions --

- (1) Interfacing with the User.

- (2) Carrying Out the Execution.

The first of these, called "Simulator Driver" interfaces with the user, accepting the commands given, analyzing for correct syntax, setting various flags and finally passing control to the simulator. The simulator itself

carries out the logical operations which represent the machine logic, testing the flags previously established for needed displays and breaks and finally returning control to the simulator driver. In a batch environment, the first function is usually managed by a deck of formatted control cards. In an interactive environment the service performed by the driver for the user is usually broader, but varies widely up to that represented by the following functions. The reader should note the similarity between this list of functions and those performed using instruments to bench check a hardware prototype.

- 1. Preventing loss of user control of the simulator.

- 2. Wide capability to set break points.

- 3. Step-wise execution.

- 4. Execution through a given number of steps.

- 5. Use of "MENUS" to set-up display patterns.

- 6. Means to change values in the simulated machine.

- 7. Display of values in registers, wires, memories.

- 8. A TRACE command to follow the execution path.

- 9. A record (history) of where execution has occurred.

The actual simulation in languages oriented around an instruction set, follows the pattern of the instruction set. They basically follow a tree like structure to arrive at the

particular instruction. When the necessary data moves or calculations are completed, the simulator is ready for the next instruction. When action is taking place concurrently in several units, as it is in most real devices, the action is more complex. Many CHDL's simply execute the logic in the order submitted using "GO TO" to provide repetition when required, while others, such as Calsim, use a table of events and provide a method of resetting the time. If concurrency is addressed, then the software system must have a way to assure that simulated concurrent actions fully represents the action without producing erroneous results.

Calsim takes the incoming logic from the description, reduces it to compressed symbology, performs a slight amount of rearranging and stores it for use by the simulator. The grammar of the stored logic is also LALR and the simulation is driven by LALR tables. At the start of execution, the "current" time points to the location in the event table where the first instruction is found. The process then proceeds through the table incrementing time and executing the logic for each component in turn. At the end the process loops back to zero time or to the pre-set time values unless the order has been changed by a RESET entry.

Synthesis of Circuits: The emphasis in the early years was to relieve the designer of the tedium of producing

electronic designs at the gate level and below which contained hundreds or even thousands of repetitions of the circuits. Sometimes such software would also generate graphics representing the logic design. System and computer design now start with medium scale integrated circuits (MSI's), large scale integrated circuits (LSI's), and very large scale integrated circuits (VLSI's), chips containing up to 100,000 gates. The original problem no longer exists in circuit design of application hardware composed of these large chips. The problem, however, is intensified in the design of the chips themselves, making this a primary The system presented here is function in that area. intended for the study of application hardware and systems using these large chips. Synthesis of circuits is not One of the other languages are addressed in this work. needed to address hardware at the switch circuit level and below.

Storage/Retrieval of Multiuse Code: While copying of stored code is rather common in programming languages, there is little mention of it in CHDL references. The use of MACROs has already been discussed. There appears to be a much greater need to apply a "copying" technique to the use of CHDL's since most system designs contain only a few components used several times. In a given facility,

activity is usually limited to two or three families of chips. Each family may have 10 to 30 members depending on the type of chip. The bit-sliced families tend to be nearer the upper value.

Miscellaneous Other Functions: The support software must perform several other functions such as:

- (1) Provide user assistance as requested.

- (2) Print tables of read-in data.

- (3) Provide documentation.

- (4) Accept and store memory content.

- (5) Provide status of certain actions.

Special Problems with a CHDL for Bit-slice Hardware

Microprogramming itself presents several special problems in designing a CHDL and the support software for the compiler and the simulator. If architecture is bit-sliced also, using the type of components found in the AMD-2900 series, TI SN-74S481 and SBP-0400A/401A or Intel 3000 series, then additional problems of handling arise. These are discussed below.

Memories: A structure for microprogramming will always

require at least one additional memory, and in many cases other ROM's (Read Only Memorys) will also be required. The contents of these memories, being essential to even minimum testing, requires that means be provided to conveniently enter the data through a file structure. The Calsim system addresses this by providing read-in capability for main, micro, and three auxiliary memories. The data for these memories can be prepared, edited by any convenient means then read into the Simcal system just prior to simulation. The values in these memories can be changed during simulation as can all data values within the system.

the von Neumon cycle built into the language in such a way that no practical way exists to avoid it. While most application designs still perform fetch/execute within the design structure, many others perform the fetch/execute at more than one level and still others do not perform fetch/execute at all, in the conventional sense. In any case, experimental architecture experiments can hardly be performed if the architecture accepted by the description language has already been partially determined. The system presented here makes no assumptions as to architecture; where the fetch/execute is used, the user simply provides it in the hardware logic of the design.

Using 2 and 4 Bit Slices: A more significant problem is the mundane handling of multiple identical cascaded chips while avoiding repetitive and burdensome bookkeeping on the part of the system user. The syntax of Calsim partially overcomes these problems. First the language represents the logic of the machine above the gate level. Second the copy statement allows copies to be made from descriptions while avoiding the burdensome task of repeating the description. The timing of these duplicates are easily modified when the copy statement is prepared, and the wiring statement allows the connections to be accomplished with little difficulty.

Pipelining and Concurrency: The problem of concurrency in structures with a CPU, memory, and a few terminals is fairly simple when addressed at the register level. When this same capability is addressed using a microprogrammable structure, the problem of concurrency becomes one of the primary problems and if pipelining is added, the problem becomes even more complex. The method used in this system has already been discussed and is in fact fairly simple. Each time event may be used by two or more components. While the clock is pointing to a particular value, the operation is completed on each component but no values are placed on the connectors to the component until all items for that time event have completed execution. At the end of

the time increment, if the outputs to a common wire do not agree, then a warning message will be given by the simulator. It is interesting to note that if a hardware prototype had been under test, no such error message would have been issued by the test equipment monitoring the test.

In pipelining, in which data is pushed into a register on one side while the previous signals already in the register are being executed from the opposite side, special effort may be needed. The user may have to set up a latch, register or other member which may not actually exist in the hardware itself or may actually exist but is not shown in the manufacturers' published descriptions.

# CHAPTER III

# MICROPROGRAMMING & MICROPROGRAMMING SUPPORT SYSTEMS

### Historical Review

Since the introduction of the microprogramming concept by Wilkes (107) machine instructions have been controlled by a series of smaller steps which in turn are controlled by a read-only memory, usually called a micromemory. The development of LSI technology with chips containing thousands of gates, has led to the design and production of the central processing unit in elements of two or four bit widths, which be assembled to any width desired. then can processing elements (CPEs'), called bit-slices, are being used more extensively in both application and computer hardware as the number of gates per chip increases (20). fact the better organization possible and the higher gate density of currently produced bipolar chips promise a change in computer organization itself (2).

A review of recent publications, concerned with bit-slice and other microprogrammable designs, reveals that most of the writers discuss simulation in terms of either specific software simulators or the use of emulators of

various types (5), (22), (58), (62). The requirements for a system to check microprogrammable hardware designs are discussed by Fuller and others in (42) and also by Gordon and Stallard in (46). The most popular way of checking a design seems to be through the use of a hardware prototype in conjuction with a logic analyzer (29), (8), (32), (65). It is proposed to substitute a software support system using the Calsim language as a basis, to perform the verification function now performed by the hardware support systems.

## Uses of the Microprogrammable Concept

The case for the use of microprogramming as a far more organized approach in the design of computers was well established in the fifties (107) (108) (109), however it was not until the development of the family of IBM 360's in the early sixties that its use came to be realized in a commercial sense. Through its use, IBM was able to develop a family of machines, all of which used the same set of assembly instructions, but varied widely in speed, capacity and price. In effect, the lower priced machines were emulating the more expensive machines.

It had long been realized that sales of newer machines could be severely delayed because of the user's huge investment in software already intact and working.

Microprogramming offered a way to overcome this problem by allowing the newer machine not only to offer all of the newer features but to also completely support the older software. This is more fully discussed by Burris in (21) and Rosin, Frieder and Eckhouse in (86).

Hewlett-Packard, among others, added to two of their models (21 and 1000) features which allowed the users to prepare and add their own instructions to those supplied with the machine. The memory was called a "writable Control Store" and could be used to prepare an instruction which could speed up execution where a time constraint problem existed. However intriguing the idea may appear on the surface, there is no indication that this has been a widely used approach to problem solution.

## MOS vs Bipolar Technology

By the mid 1970's it was apparent that MOS technology would produce a flood of microprocessor driven application devices by the early eighties. This has certainly come to pass. Texas Instruments, Intel, and Advanced Micro Devices also saw the need to organize the fundamental building blocks of the microprocessor architecture around something other than either the complete microprocessor chip, which limited design freedom or Medium Scale Integrated (MSI)

chips with 10 to 50 gates. The MSI chips included such devices as registers, latches, adders, decoders, multiplexers (2). All three companies chose to invest in Bipolar technology which was at that time at least ten times fast as the MOS technology and used larger chips with a different organization. To make the application hardware versatile, bit-slice chips were introduced which allowed the designer to vary the size of the hardware under construc-The units other than the Central Processing Element tion. included special chips for selecting the (CPE) microinstruction, priority handlers, direct memory access, front panel control, program instruction counter and input-output control.

The problem of testing and proving a microprogrammed system is more complex than a conventional machine since an additional level is involved. This means that one must test the hardware system to assure that it will perform as intended, but this must be done with a firmware sequence as yet untested. The hardware emulator and prototype model resolve this by allowing the design group to carry out tests to assure the machine will perform as intended. Meantime if the firmware which will actually drive the device is to be completed, a simulator must be constructed so that written and assembled firmware can be tested. The system presented here allows the designer to provide a system description at

the programming level while retaining hardware identity. The microprogrammer can then use a copy of the description to simulate the firmware execution. As the design develops and the hardware designer provides additional details, the hardware description is modified and the firmware rechecked to assure that the defined hardware and the firmware are still compatable.

A hierarchical design process (100) may be used by providing only functional details in the first pass, thus making the description quite close to the design specification. This can be used as a test bed for firmware (microprogram) and while it is under preparation, the hardware design can be augmented with further details in a second version of the hardware. When the firmware is complete and proven on the functional design, it can then be used to check the detailed design of the hardware.

## Assembly of Microcode

The problem of developing an assembler for microcode will not be addressed here. Each design must have special treatment for the special fields it contains and hence must be tailored for the specific design. These problems are discussed at length in (57). Once the microcode has been assembled however, it is ready for the Simcal system to use.

#### CHAPTER IV

CALSIM: COMPUTER ARCHITECTURE LANGUAGE FOR SIMULATION

Project Background

In 1977 while studying bit-sliced microprocessors, Dr. Walker suggested that there should be a way, not only to "assemble" a set of microinstructions, as was being done by the XMAS-CHROMIS system, but to also verify that the program was correct. The bit-sliced instructions, unlike machines using fixed length instructions, might be any length and have any number of different configurations. It was from this need to verify the microinstructions that this project developed.

The implementation of the project started in the fall of 1978 with a literature search, followed in the first half of 1979 with design of the language. The top level of the software support system was written in the fall of 1979 and routes the user to the various environments — the compiler, simulator, library (to search/edit), micromemory read—in, main—memory read—in, table, and documentation requests. The lexical scanner and the syntactical analyzer portions of the compiler and several of the minor modules were completed in the spring of 1980. Work on the semantic code generator was completed in the summer of 1980, allowing the compiler to be

used on a trial basis during the fall semester. Revisions, based on input from the students, were completed the next semester. Work on the simulator was completed during the summer of 1981. Preparation of the dissertation extended from August 1981 through September 1982. The grammar was rewritten in August, 1982 and the final modifications of the software was made during June though September 1982.

# The Requirements for the Grammar

The requirements for Calsim were largely developed before the Calsim language was written the first time using the characteristics found in other CHDL's. These were adopted, extended, and modified as appropriate. Each of the appropriate articles were also searched for descriptions of weaknesses in other languages and suggested extensions. These were collected and used in preparing this list of requirements. The last significant changes to the grammar were made as new aspects of CHDL's became apparent during the preparation of this thesis.

1. The grammar of the language must be LALR (Look Ahead Left Right) so that support for verification and syntactical analysis of the grammar can be performed on an available grammar analyzer. This assures a cohe-

sive, more easily maintained language and a compiler/

simulator with fewer errors than use of ad hoc methods.

The superiority of compilers written using formal

methods is now well established in the area of programming languages (6). The same superiority is true of

CHDL's.

- 2. The language must be free form to save the user the bother of rigid formatting. The text must extend from column 1 through column 80 using space or spaces as delimiters for the words of the language, just as natural languages use spaces.

- 3. The language must be capable of describing a hierarchical structure so that representation will be similar to the hardware. This representation is to be centered around a "system" but must also accept collections of systems. The description should closely parallel real hardware and be capable of describing logic and storage from the bit level upward.

- 4. The grammar must not contain features which presume a pre-determined architecture.

- 5. The language must support comment insertion into

the middle of text as well as full lines. This must be accomplished in an easy and natural way.

- 6. The grammar must allow descriptions of registers, subregisters, and cascaded registers of any practical length and subscripted to one level if desired.

- 7. The language must be statement oriented making the task of preparing the description easier for the user.

- 8. The grammar must provide capability to describe parallel operations so simulation is realistic.

- 9. The grammar must provide timing ability so that the asynchronous operations and interrupts can be simulated to the level of user interest. The timing must allow the logic to repeat operations until the specified conditions are fulfilled thus duplicating a "HOLD" condition in the hardware.

- 10. There must be provision to use micromemory, main memory, and at least three auxiliary memories copied from external files.

- 11. The system must provide capability to develop data

to fill the memory files separately and provisions to "read" the data into the system when the file is complete either before or during simulation.

- 12. The language must provide special features for ports (terminals) so that data passing through the terminal will be converted to ASCII as received at the terminal and from ASCII as sent from the terminal.

- 13. The grammar must support entries to and retrieval of descriptions from a library. The copy ability must include provisions to store complete descriptions during compilation and to retrieve the description during that compilation or a subsequent compilation. The library must be accessable for listings and searches of the contents from an area of the software other than the compiler itself. The time events stored in the component description must also be adjusted at the same time the item is copied, using the content of the copy command to determine the new event times.

- 14. The grammar must provide for entry of multiple components of the same type with minimum difficulty. The use of multiple components in bit-sliced and conventional microprocessors require that this be done

to reduce the time used for multiple entries.

- 15. The grammar must provide for logic description in a way most likely to be in the language of the user, such as found in Fortran, Algol, or PL/I.

- 16. The language must provide for connectors and sets of connectors between the components so that output from one component may be either held or transferred to another component in a manner similar to hardware.

- 17. The language must provide for a start condition. This will consist of a way to set wires, registers, pins, and memories to specified values so the device can begin execution.

- 18. Language construction which allows the compiler to perform work which in fact must be done in hardware must be avoided or be made apparent to the user.

## The Grammar -- Development

The grammar for the Calsim language is LALR (look ahead left right) and was developed using a grammar analyzer by LaLonde (63) which resides on the UTA IBM-4341. The

LaLonde analyzer verifies the grammar as meeting the requirements of an LALR (K=1) grammar and produces tables which control the execution of the syntax analyzer.

The constuction of the grammar itself, is somtimes better understood by looking at the language examples. These may be found in abundance in Appendix 3 of the User's Manual (Appendix 6). The Backus Normal Form productions (BNF) are shown in their entirety in Appendix 3.